Application

**RV-8063-C8**

**Application Manual**

# Manual

# **RV-8063-C8**

## Ultra-Small Real-Time Clock Module with SPI-Bus Interface

#### **TABLE OF CONTENTS**

| 1. | 0             | VERVIEW                                               | 4    |

|----|---------------|-------------------------------------------------------|------|

|    | 1.1.          | GENERAL DESCRIPTION                                   | 4    |

|    | 1. <b>2</b> . | APPLICATIONS                                          | 5    |

|    | 1.3.          | ORDERING INFORMATION                                  | 5    |

| 2. | BI            | LOCK DIAGRAM                                          | 6    |

|    | 2.1.          | PINOUT                                                | 7    |

|    | 2.2.          | PIN DESCRIPTION                                       | 7    |

|    | 2.3.          | FUNCTIONAL DESCRIPTION                                | 8    |

|    | 2.4.          | DEVICE PROTECTION DIAGRAM                             | 9    |

| 3. | R             | EGISTER ORGANIZATION                                  | . 10 |

|    | 3.1.          | REGISTER OVERVIEW                                     | . 10 |

|    | 3.2.          | CONTROL REGISTERS                                     | . 11 |

|    | 3.3.          | TIME AND DATE REGISTERS                               | . 14 |

|    | 3.4.          | ALARM REGISTERS                                       | . 17 |

|    | 3.5.          | TIMER REGISTERS                                       | . 20 |

|    | 3.6.          | REGISTER RESET VALUES SUMMARY                         | . 21 |

| 4. | D             | ETAILED FUNCTIONAL DESCRIPTION                        | . 22 |

|    | 4.1.          | POWER ON RESET (POR)                                  | . 22 |

|    | 4.2.          | SOFTWARE RESET                                        | . 22 |

|    | 4.3.          | OSCILLATOR STOP FLAG                                  | . 23 |

|    | 4.4.          | SETTING AND READING THE TIME                          | . 24 |

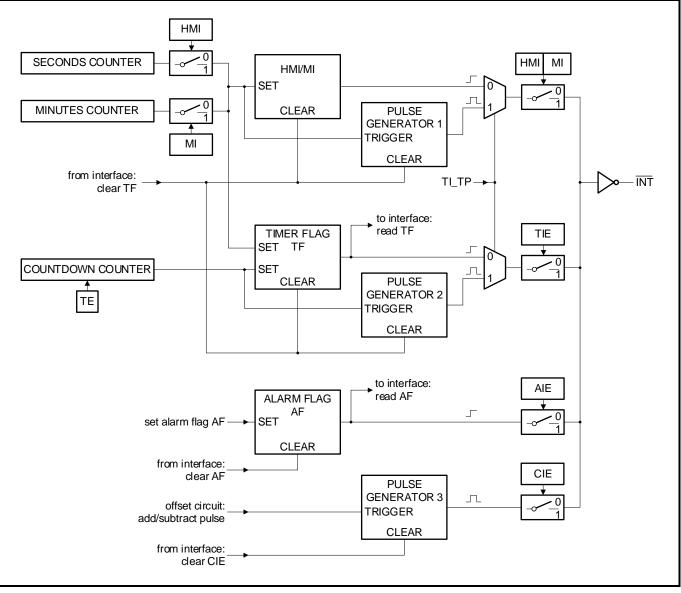

|    | 4.5.          | INTERRUPT OUTPUT                                      | . 25 |

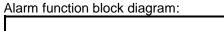

|    | 4.6.          | ALARM FUNCTION                                        | . 26 |

|    | 4.            | 6.1. ALARM INTERRUPT                                  | . 26 |

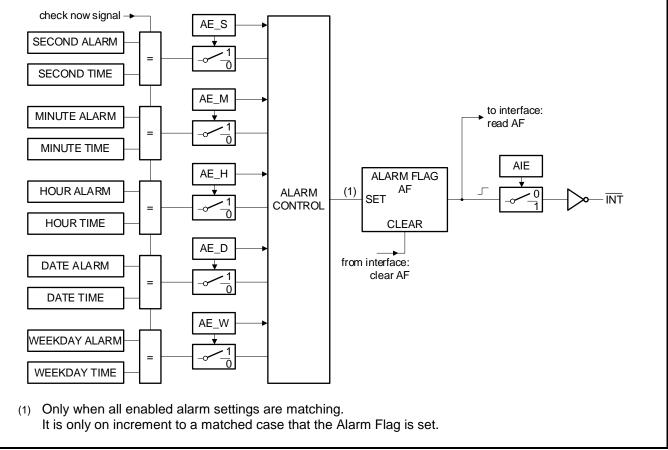

|    | 4.7.          | COUNTDOWN TIMER FUNCTION                              | . 27 |

|    | 4.            | 7.1. TIMER FLAG TF                                    | . 27 |

|    | 4.            | 7.2. TIMER INTERRUPT MODE TI_TP                       | . 27 |

|    | 4.            | 7.3. PULSE GENERATOR 2                                | . 27 |

|    | 4.            | 7.4. USE OF THE COUNTDOWN TIMER                       | . 28 |

|    | 4.8.          | MINUTE AND HALF MINUTE INTERRUPT FUNCTION             | . 30 |

|    | 4.            | 8.1. PULSE GENERATOR 1                                | . 30 |

|    | 4.9.          | FREQUENCY OFFSET COMPENSATION                         | . 31 |

|    | 4.            | 9.1. OFFSET COMPENSATION CALCULATION WORKFLOW         | . 32 |

|    |               | COMPENSATION INTERRUPT FUNCTION                       |      |

|    | 4.            | 10.1. COMPENSATION PULSES WHEN MODE = 0 (NORMAL MODE) | . 34 |

|    | 4.            | 10.2. COMPENSATION PULSES WHEN MODE = 1 (FAST MODE)   | . 35 |

|    | 4.11.         | CLKOUT FREQUENCY SELECTION                            | . 36 |

|    | 4.12.         | STOP BIT FUNCTION                                     | . 37 |

Micro Crystal

Ultra-Small Real-Time Clock Module with SPI-Bus Interface

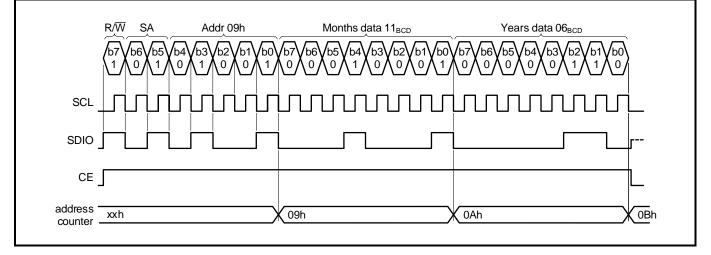

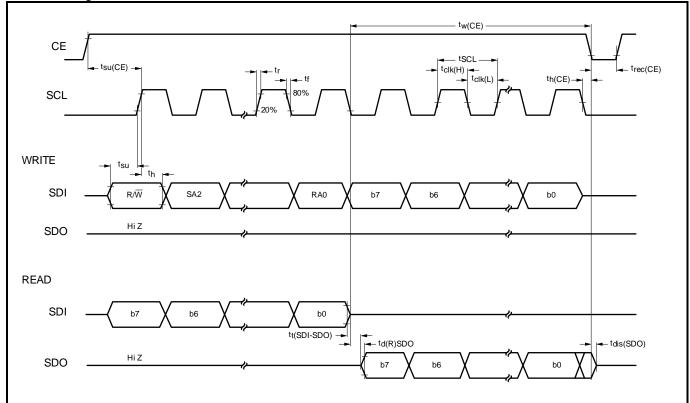

| 5. | S           | PI INTERFACE                                                 | 39   |

|----|-------------|--------------------------------------------------------------|------|

|    | 5.1.        | SERIAL BUS READ / WRITE EXAMPLES                             | 40   |

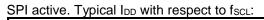

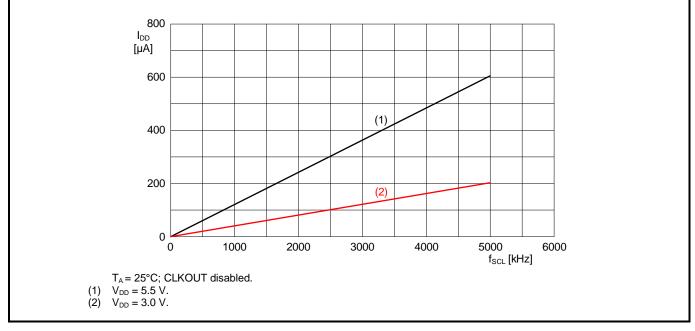

| 6. | E           | ELECTRICAL SPECIFICATIONS                                    | 41   |

|    | 6.1.        | ABSOLUTE MAXIMUM RATINGS                                     | . 41 |

|    | 6.2.        | OPERATING PARAMETERS                                         | . 42 |

|    | 6.3.        | OSCILLATOR PARAMETERS                                        | . 45 |

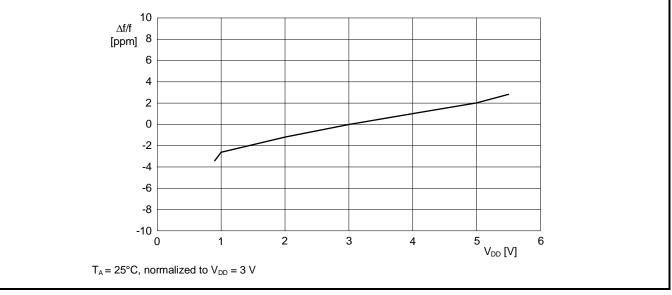

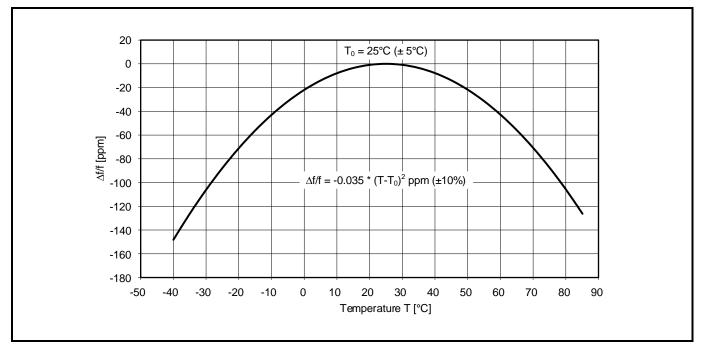

|    | 6           | 3.3.1. XTAL FREQUENCY VS. TEMPERATURE CHARACTERISTICS        | 45   |

|    | 6.4.        | SPI-BUS CHARACTERISTICS                                      | 46   |

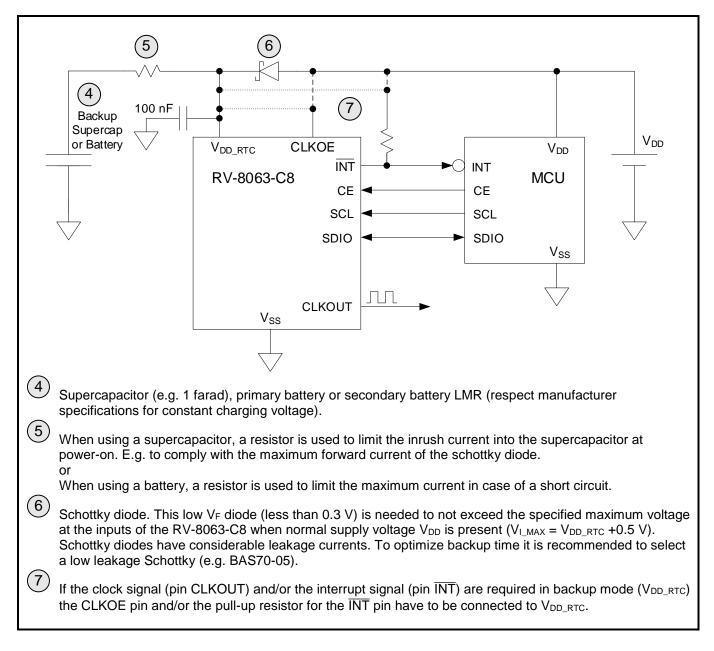

| 7. | A           | APPLICATION INFORMATION                                      | 47   |

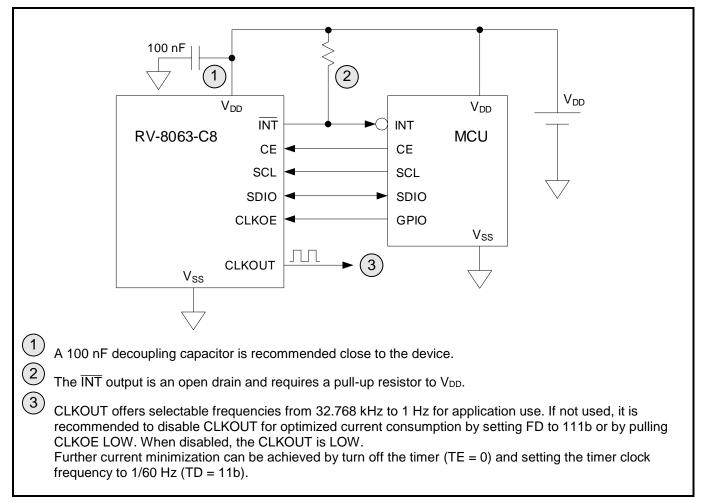

|    | 7.1.        | OPERATING RV-8063-C8                                         | 47   |

|    | 7.2.        | OPERATING RV-8063-C8 WITH BACKUP CAPACITOR                   | 48   |

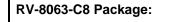

| 8. | F           | PACKAGE                                                      | 49   |

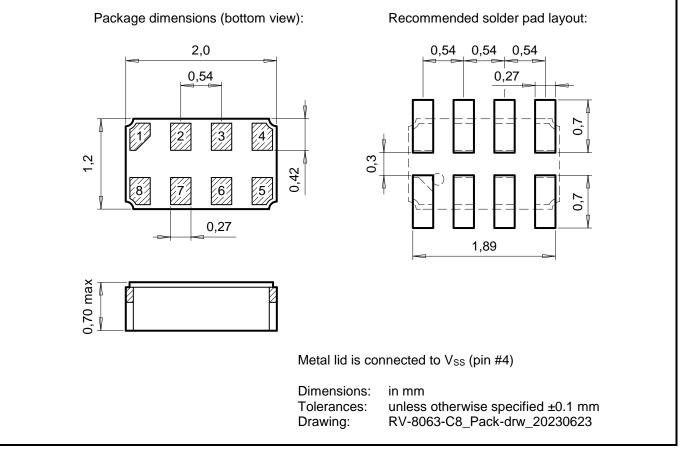

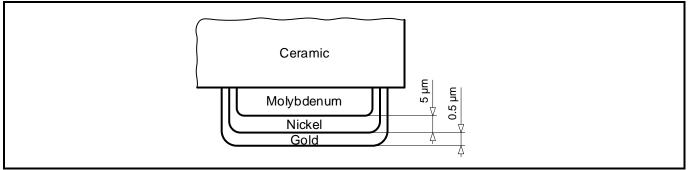

|    | 8.1.        | DIMENSIONS AND SOLDER PAD LAYOUT                             | . 49 |

|    | 8           | 3.1.1. RECOMMENDED THERMAL RELIEF                            | 49   |

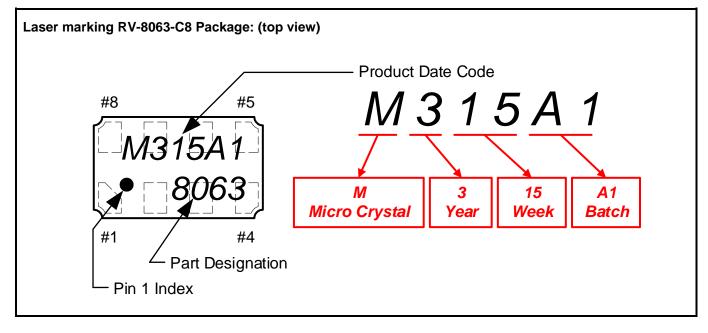

|    | 8.2.        | MARKING AND PIN #1 INDEX                                     | . 50 |

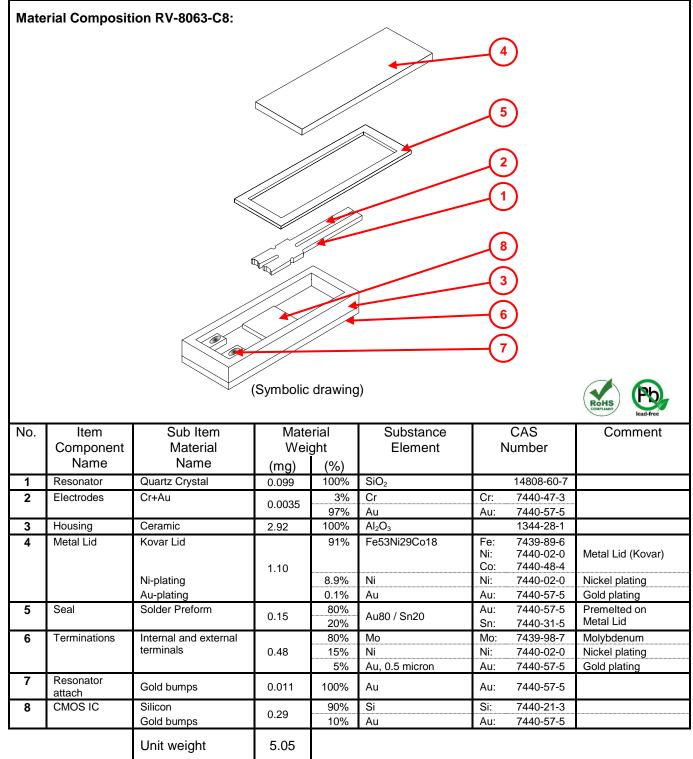

| 9. | Ν           | IATERIAL COMPOSITION DECLARATION & ENVIRONMENTAL INFORMATION | 51   |

|    | 9.1.        | HOMOGENOUS MATERIAL COMPOSITION DECLARATION                  | . 51 |

|    | 9.2.        | MATERIAL ANALYSIS & TEST RESULTS                             | . 52 |

|    | 9.3.        | RECYCLING MATERIAL INFORMATION                               | 53   |

|    | 9.4.        | ENVIRONMENTAL PROPERTIES & ABSOLUTE MAXIMUM RATINGS          | 54   |

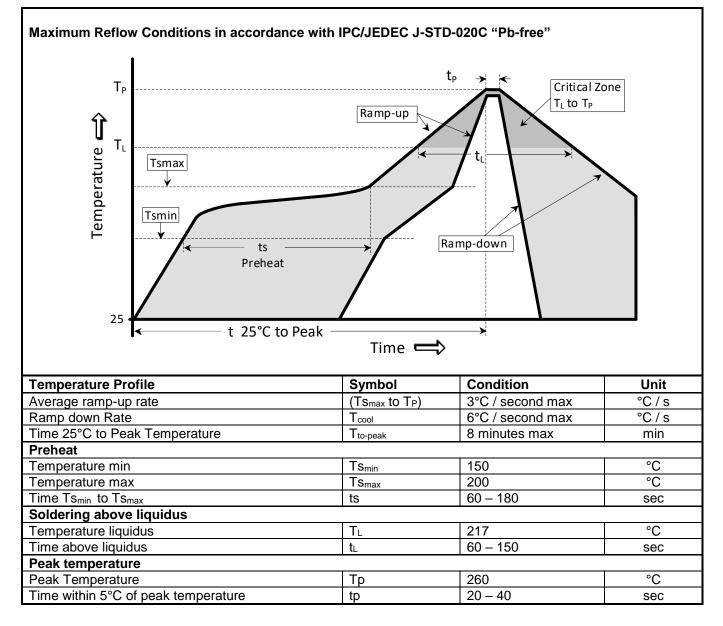

| 1( | ). S        | SOLDERING INFORMATION                                        | 55   |

| 11 | I. F        | ANDLING PRECAUTIONS FOR MODULES WITH EMBEDDED CRYSTALS       | 56   |

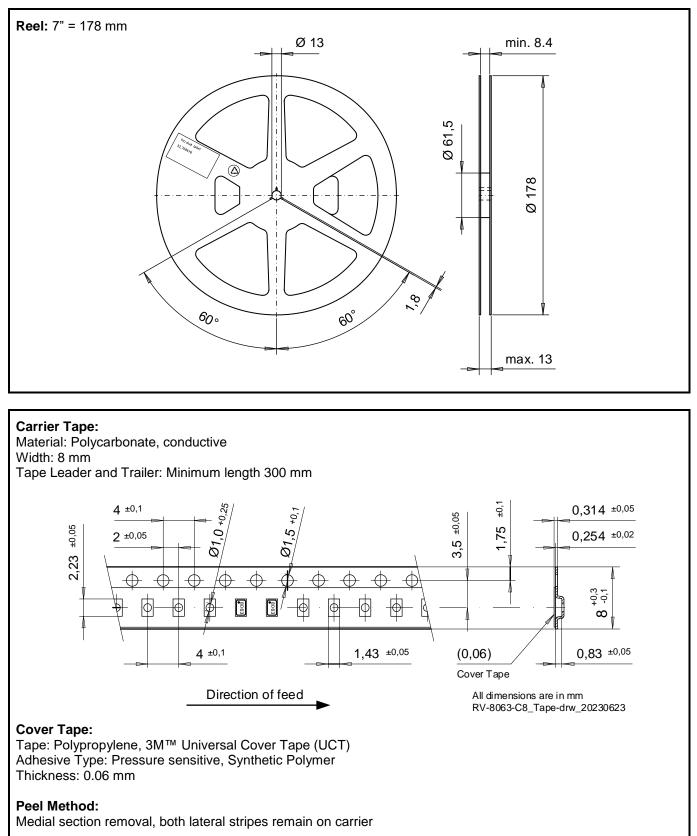

| 12 | 2. F        | PACKING & SHIPPING INFORMATION                               | 57   |

| 13 | з. <b>с</b> | COMPLIANCE INFORMATION                                       | 58   |

| 14 | 4. C        | DOCUMENT REVISION HISTORY                                    | 58   |

### RV-8063-C8

#### Ultra-Small Real-Time Clock Module with SPI-Bus Interface

#### 1. OVERVIEW

- RTC module with built-in "Tuning Fork" crystal oscillating at 32.768 kHz

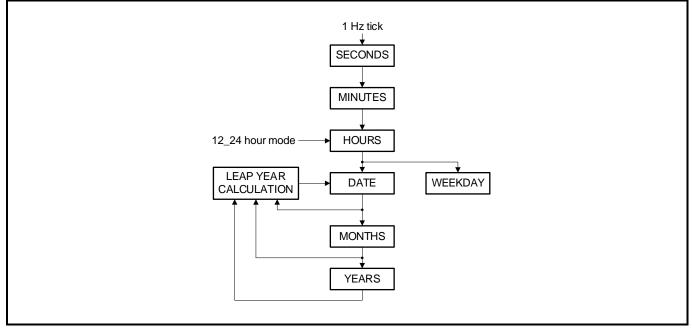

- Counters for seconds, minutes, hours, date, weekday, month and year

- Programmable Offset register for frequency adjustment

- Automatic leap year calculation (2000 to 2099)

- Alarm Interrupts for second, minutes, hour, date and weekday settings

- Countdown Timer Interrupt function

- Minute and Half Minute Interrupt

- Oscillator stop detection function

- Internal Power-On Reset (POR)

- Programmable Clock Output for peripheral devices (32.768 kHz, 16.384 kHz, 8.192 kHz, 4.096 kHz, 2.048 kHz, 1.024 kHz and 1 Hz) with enable/disable function (CLKOE)

- 3 line SPI-bus with a maximum data rate of 7 Mbit/s

- Wide operating voltage range: 0.9 V to 5.5 V

- Wide interface operating voltage: 1.8 to 5.5 V

- Very low current consumption: 190 nA ( $V_{DD} = 3.0 \text{ V}, T_A = 25^{\circ}\text{C}$ )

- Operating temperature range: -40 to +85°C

- Ultra-miniature ceramic SMD package with metal lid, RoHS-compliant and 100% lead-free: 2.0 x 1.2 x 0.70 mm

- Ultra-low profile (maximum height 0.70 mm), lightweight (5.1 mg)

- Automotive qualification according to AEC-Q200 available

#### 1.1. GENERAL DESCRIPTION

The RV-8063-C8 is a CMOS real-time clock/calendar module optimized for low power consumption. An Offset register makes it possible to compensate for the frequency deviation of the clock of 32.768 kHz. All addresses and data are transferred serially via a Serial Peripheral Interface (SPI-bus) with a maximum data rate of 7 Mbit/s. The register address is incremented automatically after each written or read data byte.

This ultra-small and lightweight RTC module has been specially designed for miniature and cost sensitive high volume applications.

#### 1.2. APPLICATIONS

The RV-8063-C8 RTC module combines standard RTC functions in high reliable, ultra-small ceramic package:

- Smallest RTC module (embedded XTAL) in miniature 2.0 x 1.2 x 0.70 mm lead-free ceramic package

- Price competitive

The unique size and the competitive pricing make this product perfectly suitable for many applications where high circuit density or a smaller PCB is required:

- Communication: IoT / Wearables / Wireless Sensors and Tags / Handsets

- Automotive: M2M / Navigation & Tracking Systems / Dashboard / Tachometers / Engine Controller Car Audio & Entertainment Systems

- Metering: E-Meter / Heating Counter / Smart Meters / PV Converter

- Outdoor: ATM & POS systems / Surveillance & Safety systems / Ticketing Systems

- Medical: Glucose Meter / Health Monitoring Systems

- Safety: Security & Camera Systems / Door Lock & Access Control

- Consumer: Gambling Machines / TV & Set Top Boxes / White Goods

- Automation: PLC / Data Logger / Home & Factory Automation / Industrial and Consumer Electronics

#### **1.3. ORDERING INFORMATION**

Example: RV-8063-C8 TA QC

| Code          | Operating temperature range |

|---------------|-----------------------------|

| TA (Standard) | -40 to +85°C                |

| Code          | Qualification             |

|---------------|---------------------------|

| QC (Standard) | Commercial Grade          |

| QA            | Automotive Grade AEC-Q200 |

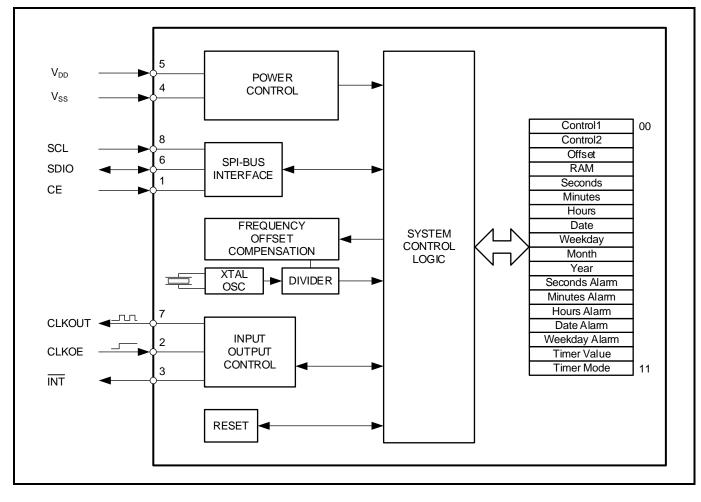

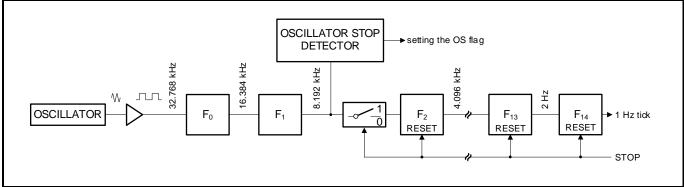

#### 2. BLOCK DIAGRAM

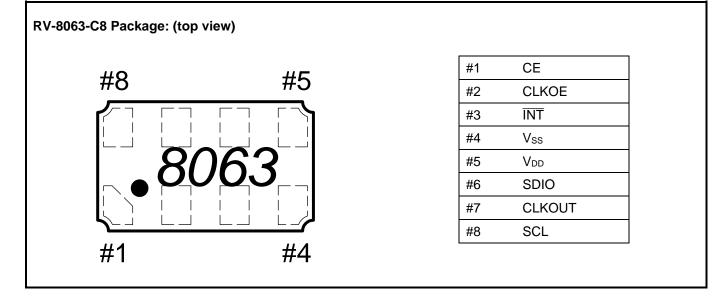

#### 2.1. PINOUT

#### 2.2. PIN DESCRIPTION

| Symbol          | Pin # | Description                                                                                                                                                                                                                                                                                |

|-----------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CE              | 1     | Chip Enable Input; when LOW, the interface is reset; may not be wired permanently HIGH.                                                                                                                                                                                                    |

| CLKOE           | 2     | Input to enable the CLKOUT pin. If CLKOE is HIGH, the CLKOUT pin is in output mode. When CLKOE is tied to Ground, the CLKOUT pin is LOW.                                                                                                                                                   |

| ĪNT             | 3     | Interrupt Output; open-drain; active LOW; requires pull-up resistor; Used to output alarm, minute, half minute, countdown timer and compensation Interrupt signals.                                                                                                                        |

| V <sub>SS</sub> | 4     | Ground.                                                                                                                                                                                                                                                                                    |

| V <sub>DD</sub> | 5     | Power Supply Voltage.                                                                                                                                                                                                                                                                      |

| SDIO            | 6     | Serial Data Input and Output.         Input:       When CE is LOW, input may float.         Output:       Push-pull output; drives from $V_{SS}$ to $V_{DD}$ ; is high-impedance when not driving.                                                                                         |

| CLKOUT          | 7     | Clock Output; push-pull; controlled by CLKOE. If CLKOE is HIGH (V <sub>DD</sub> ), the CLKOUT pin drives the square wave of 32.768 kHz, 16.384 kHz, 8.192 kHz, 4.096 kHz, 2.048 kHz, 1.024 kHz or 1 Hz (Default value is 32.768 kHz). When CLKOE is tied to Ground, the CLKOUT pin is LOW. |

| SCL             | 8     | Serial Clock Input. When CE is LOW, this input may float.                                                                                                                                                                                                                                  |

#### 2.3. FUNCTIONAL DESCRIPTION

The RV-8063-C8 is a low power CMOS real-time clock/calendar module with embedded 32.768 kHz Crystal. The CMOS IC contains 18 8-bit registers with an auto-incrementing register address, a frequency divider which provides the source clock for the Real Time Clock (RTC), a programmable clock output, and an SPI-bus with a maximum data rate of 7 Mbit/s. The Offset register allows to digitally adjust the 32.768 kHz oscillator frequency in order to compensate and minimize time deviation.

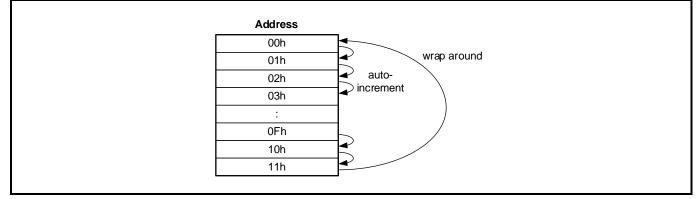

The built-in address register will increment automatically after each read or write of a data byte up to the register 11h. After register 11h, the auto-incrementing will wrap around to address 00h (see following Figure).

#### Handling address registers:

All registers (see REGISTER OVERVIEW) are designed as addressable 8-bit parallel registers although not all bits are implemented.

- The first two registers (memory address 00h and 01h) are used as control and status register.

- The register at address 02h is an Offset register allowing the compensation of time deviation.

- The register at address 03h is a free User RAM byte.

- The addresses 04h through 0Ah are used as counters for the clock function (seconds up to year counters).

- Address locations 0Bh through 0Fh contain alarm registers which define the conditions for an alarm.

- The registers at 10h and 11h are for the timer function.

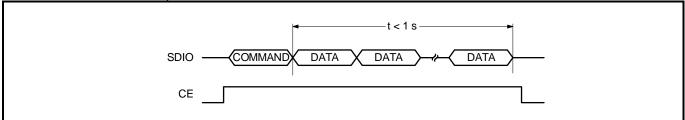

The Seconds, Minutes, Hours, Date, Month and Year as well as the corresponding alarm registers are all coded in Binary Coded Decimal (BCD) format. When one of the RTC registers is written or read, the contents of all time counters are frozen. Therefore, faulty writing or reading of the clock and calendar during a carry condition is prevented for up to 1 second.

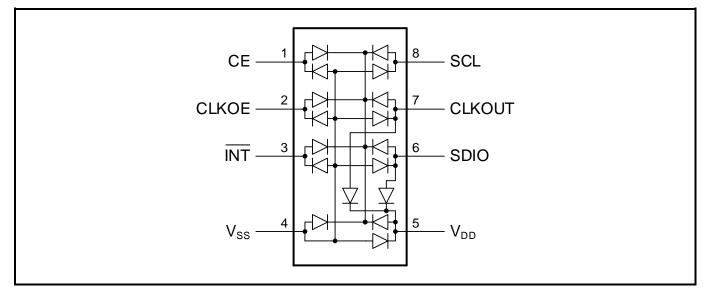

#### 2.4. DEVICE PROTECTION DIAGRAM

#### 3. REGISTER ORGANIZATION

Registers are accessed by selecting a register address and then performing read or write operations. Multiple reads or writes may be executed in a single access, with the address automatically incrementing after each byte.

18 registers (00h – 11h) are available. The time registers are encoded in the Binary Coded Decimal format (BCD) to simplify application use. Other registers are either bit-wise or standard binary format. When one of the RTC registers is written or read, the contents of all time counters are frozen for up to 1 second. Therefore, faulty writing or reading of the clock and calendar during a carry condition is prevented.

#### 3.1. REGISTER OVERVIEW

After reset, all registers are set according to Table in section REGISTER RESET VALUES SUMMARY.

| Address              | Function                      | Bit 7              | Bit 6       | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |

|----------------------|-------------------------------|--------------------|-------------|-------|-------|-------|-------|-------|-------|--|--|

| 00h                  | Control1                      | TEST               | SR          | STOP  | S     | R     | CIE   | 12_24 | CAP   |  |  |

| 01h                  | Control2                      | AIE                | AF          | MI    | HMI   | TF    | FD    |       |       |  |  |

| 02h                  | Offset                        | MODE               | MODE OFFSET |       |       |       |       |       |       |  |  |

| 03h                  | RAM                           |                    | RAM data    |       |       |       |       |       |       |  |  |

| 04h                  | Seconds                       | OS                 | 40          | 20    | 10    | 8     | 4     | 2     | 1     |  |  |

| 05h                  | Minutes                       | Х                  | 40          | 20    | 10    | 8     | 4     | 2     | 1     |  |  |

| OCh                  | Hours (24 hour)               | X                  | х           | 20    | 10    | 8     | 4     | 2     | 1     |  |  |

| 06h                  | Hours (12 hour)               | ^                  |             | AMPM  | 10    | 8     | 4     | 2     | 1     |  |  |

| 07h                  | Date                          | Х                  | Х           | 20    | 10    | 8     | 4     | 2     | 1     |  |  |

| 08h                  | Weekday                       | Х                  | Х           | Х     | Х     | Х     | 4     | 2     | 1     |  |  |

| 09h                  | Month                         | Х                  | Х           | Х     | 10    | 8     | 4     | 2     | 1     |  |  |

| 0Ah                  | Year                          | 80                 | 40          | 20    | 10    | 8     | 4     | 2     | 1     |  |  |

| 0Bh                  | Seconds Alarm                 | AE_S               | 40          | 20    | 10    | 8     | 4     | 2     | 1     |  |  |

| 0Ch                  | Minutes Alarm                 | AE_M               | 40          | 20    | 10    | 8     | 4     | 2     | 1     |  |  |

| ODh                  | Hours Alarm (24h)             |                    | V           | 20    | 10    | 8     | 4     | 2     | 1     |  |  |

| 0Dh                  | Hours Alarm (12h)             | AE_H               | Х           | AMPM  | 10    | 8     | 4     | 2     | 1     |  |  |

| 0Eh                  | Date Alarm                    | AE_D               | Х           | 20    | 10    | 8     | 4     | 2     | 1     |  |  |

| 0Fh                  | Weekday Alarm                 | AE_W               | Х           | Х     | Х     | Х     | 4     | 2     | 1     |  |  |

| 10h                  | Timer Value                   | 128                | 64          | 32    | 16    | 8     | 4     | 2     | 1     |  |  |

| 11h                  | Timer Mode                    | Х                  | Х           | Х     | Т     | D     | TE    | TIE   | TI_TP |  |  |

| Bit positions labele | d as X are not implemented ar | nd will return a ( | ) when read | d.    |       |       |       |       |       |  |  |

#### 3.2. CONTROL REGISTERS

To ensure that all control registers will be set to their default values, the  $V_{DD}$  level must be at zero volts at initial power-up. If this is not possible, a reset must be initiated with the software reset command when power is stable. Refer to section SOFTWARE RESET for details.

#### 00h - Control1

Control and status register 1.

| Address | Function | Bit 7                                                                                                                                       | Bit 6                                                                                                            | Bit 5                         | Bit 4         | Bit 3                        | Bit 2       | Bit 1        | Bit 0      |  |  |

|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------------------------------|---------------|------------------------------|-------------|--------------|------------|--|--|

| 00h     | Control1 | TEST                                                                                                                                        | SR                                                                                                               | STOP                          | S             | R                            | CIE         | 12_24        | CAP        |  |  |

| 0011    | Reset    | 0                                                                                                                                           | 0                                                                                                                | 0                             | 0             | 0                            | 0           | 0            | 0          |  |  |

| Bit     | Symbol   | Value                                                                                                                                       |                                                                                                                  |                               |               | Descriptior                  | า           |              |            |  |  |

| 7       | TEST     | 0                                                                                                                                           | Normal n                                                                                                         | node.                         |               |                              |             |              |            |  |  |

| 7       | 1231     | 1                                                                                                                                           | External                                                                                                         | clock test m                  | node. Do no   | ot use.                      |             |              |            |  |  |

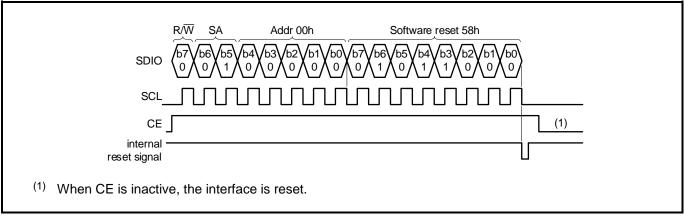

|         |          |                                                                                                                                             |                                                                                                                  | Software I                    | Reset (see    | SOFTWAR                      | E RESET)    |              |            |  |  |

| 6       | SR       | 0                                                                                                                                           | No softwa                                                                                                        | are reset.                    |               |                              |             |              |            |  |  |

|         |          | 1                                                                                                                                           |                                                                                                                  | 011000 (58                    | h) must be    | ways return<br>sent to regis | ster Contro |              | a software |  |  |

|         | STOP     |                                                                                                                                             |                                                                                                                  | STOP b                        | oit (see STC  | OP BIT FUN                   | CTION)      |              |            |  |  |

| -       |          | 0 RTC clock runs.                                                                                                                           |                                                                                                                  |                               |               |                              |             |              |            |  |  |

| 5       |          | RTC clock is stopped; the upper part of the RTC divider chain flip-flops                                                                    |                                                                                                                  |                               |               |                              |             |              |            |  |  |

|         |          | 1 (prescaler F2 to F14) are asynchronously set logic 0. The CLKOUT<br>frequencies 32.768 kHz, 16.384 kHz and 8.192 kHz are still available. |                                                                                                                  |                               |               |                              |             |              |            |  |  |

|         |          | Software Reset (see SOFTWARE RESET)                                                                                                         |                                                                                                                  |                               |               |                              |             |              |            |  |  |

| 4:3     | SR       | 00                                                                                                                                          | No softwa                                                                                                        | are reset.                    |               |                              | - /         |              |            |  |  |

| 4.5     | SK .     | 11                                                                                                                                          | 1 Initiate software reset; this bits always returns a 0 w<br>software reset, 01011000 (58h) must be sent to regi |                               |               |                              |             |              |            |  |  |

|         |          | Comp                                                                                                                                        | ensation In                                                                                                      | terrupt Enal                  | ole (see FR   | EQUENCY                      | OFFSET C    | OMPENSA      | TION)      |  |  |

| 2       | CIE      | 0                                                                                                                                           | No comp                                                                                                          | ensation int                  | errupt will l | be generate                  | d.          |              |            |  |  |

| L       |          | 1                                                                                                                                           |                                                                                                                  | sation interr<br>ation cycle. |               | will be gene                 | rated on pi | n INT at eve | ery        |  |  |

|         |          | 12 or 24                                                                                                                                    |                                                                                                                  |                               |               | E REGISTE                    | RS and AL   | ARM REGI     | STERS)     |  |  |

| 1       | 12_24    | 0                                                                                                                                           | 24 hour r                                                                                                        | node is sele                  | ected (0 to 2 | 23).                         |             |              |            |  |  |

|         |          | 1                                                                                                                                           | 12 hour r                                                                                                        | node is sele                  | ected (1 to   | 12).                         |             |              |            |  |  |

| 0       | CAP      | 0                                                                                                                                           | 0 Must always be written with logic 0.                                                                           |                               |               |                              |             |              |            |  |  |

#### 01h - Control2

Control and status register 2.

| Address             | Function                        | Bit 7                                                                       | Bit 6                                   | Bit 5                      | Bit 4                    | Bit 3                  | Bit 2     | Bit 1     | Bit 0   |  |  |  |

|---------------------|---------------------------------|-----------------------------------------------------------------------------|-----------------------------------------|----------------------------|--------------------------|------------------------|-----------|-----------|---------|--|--|--|

| 01h                 | Control2                        | AIE                                                                         | AF                                      | MI                         | HMI                      | TF                     |           | FD        |         |  |  |  |

| UIII                | Reset                           | 0                                                                           | 0                                       | 0                          | 0                        | 0                      | 0         | 0         | 0       |  |  |  |

| Bit                 | Symbol                          | Value                                                                       |                                         |                            |                          | Descriptio             | n         |           |         |  |  |  |

|                     |                                 | Alar                                                                        | m Interrupt                             | Enable (se                 | e ALARM F                | UNCTION                | and INTER | RUPT OU   | (PUT)   |  |  |  |

| 7                   | AIE                             | 0                                                                           | D Disabled                              |                            |                          |                        |           |           |         |  |  |  |

|                     |                                 | 1                                                                           | Enabled                                 |                            |                          |                        |           |           |         |  |  |  |

|                     |                                 |                                                                             |                                         |                            | RM FUNC                  | TION and IN            | NTERRUP   | FOUTPUT)  |         |  |  |  |

| 6                   | AF                              | 0                                                                           | Read: Ala<br>Write: Ala                 |                            |                          |                        |           |           |         |  |  |  |

|                     |                                 | 1                                                                           |                                         | arm Flag ac<br>arm Flag re | tive<br>mains unch       | anged                  |           |           |         |  |  |  |

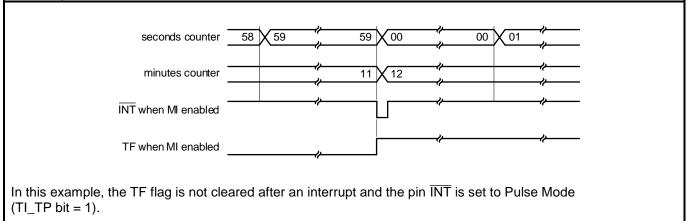

|                     |                                 | Minute I                                                                    | nterrupt En                             | able (see N                | 1INUTE AN                | D HALF MI<br>R FLAG TF |           | ERRUPT F  | UNCTION |  |  |  |

| 5                   | MI                              | 0                                                                           | Disabled                                |                            |                          |                        | /         |           |         |  |  |  |

|                     |                                 | 1                                                                           | Enabled                                 |                            |                          |                        |           |           |         |  |  |  |

|                     |                                 | Half                                                                        | Minute Inte                             |                            | le (see MIN<br>CTION and |                        |           | JTE INTER | RUPT    |  |  |  |

| 4                   | HMI                             | 0                                                                           | Disabled                                |                            |                          |                        |           |           |         |  |  |  |

|                     |                                 | 1                                                                           | Enabled                                 |                            |                          |                        |           |           |         |  |  |  |

|                     |                                 | Timer Flag (see COUNTDOWN TIMER FUNCTION, INTERRUPT OUTPU<br>TIMER FLAG TF) |                                         |                            |                          |                        |           |           |         |  |  |  |

| 3                   | TF                              | 0                                                                           | No timer interrupt generated            |                            |                          |                        |           |           |         |  |  |  |

|                     |                                 | 1                                                                           | Flag set when timer interrupt generated |                            |                          |                        |           |           |         |  |  |  |

| 2:0                 | FD                              | 000 to<br>111                                                               | CLKOUT                                  | Frequency                  | (see CLKC                | OUT FREQU              | JENCY SE  | LECTION)  |         |  |  |  |

| FD                  |                                 |                                                                             | CL                                      | KOUT Free                  | quency                   |                        |           |           |         |  |  |  |

| 000                 | 32.768 kHz – Default value      |                                                                             |                                         |                            |                          |                        |           |           |         |  |  |  |

| 001                 | 16.384 kHz                      |                                                                             |                                         |                            |                          |                        |           |           |         |  |  |  |

| 010                 | 8.192 kHz                       |                                                                             |                                         |                            |                          |                        |           |           |         |  |  |  |

| 011                 | 4.096 kHz                       |                                                                             |                                         |                            |                          |                        |           |           |         |  |  |  |

| 100                 | 2.048 kHz                       |                                                                             |                                         |                            |                          |                        |           |           |         |  |  |  |

| 101                 | 1.024 kHz                       |                                                                             |                                         |                            |                          |                        |           |           |         |  |  |  |

| 110                 | 1 Hz <sup>(1)</sup>             |                                                                             |                                         |                            |                          |                        |           |           |         |  |  |  |

| 111                 | CLKOUT = LOW                    |                                                                             |                                         |                            |                          |                        |           |           |         |  |  |  |

| 1) 1 Hz clock pulse | es are affected by compensation | oulses (see                                                                 | FREQUEN                                 | CY OFFSE                   | T COMPE                  | NSATION).              |           |           |         |  |  |  |

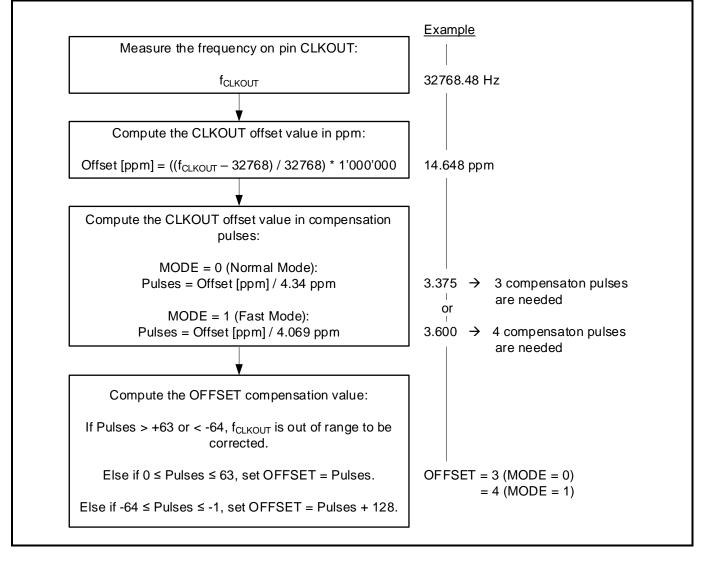

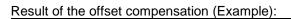

#### 02h – Offset Register

This register holds the OFFSET value to digitally compensate the initial frequency deviation of the 32.768 kHz oscillator or for aging adjustment (see FREQUENCY OFFSET COMPENSATION).

| Address | Function            | Bit 7                                   | Bit 6                                                                                                                                                                                                                                                                                                                                   | Bit 5       | Bit 4       | Bit 3        | Bit 2                                            | Bit 1 | Bit              |  |

|---------|---------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|--------------|--------------------------------------------------|-------|------------------|--|

| 02h     | Offset              | MODE                                    |                                                                                                                                                                                                                                                                                                                                         |             |             | OFFSET       |                                                  |       |                  |  |

| 0211    | Reset               | 0                                       | 0                                                                                                                                                                                                                                                                                                                                       | 0           | 0           | 0            | 0                                                | 0     |                  |  |

| Bit     | Symbol              | Value                                   | Value Description                                                                                                                                                                                                                                                                                                                       |             |             |              |                                                  |       |                  |  |

|         |                     |                                         |                                                                                                                                                                                                                                                                                                                                         |             | Offset      | Mode         |                                                  |       |                  |  |

| 7       | MODE                | 0                                       | Normal N                                                                                                                                                                                                                                                                                                                                | lode: Offse | t is made o | nce every ti | vo hours.                                        |       |                  |  |

|         |                     | 1                                       | Fast Mode: Offset is made every 4 minutes.                                                                                                                                                                                                                                                                                              |             |             |              |                                                  |       |                  |  |

| 6:0     | OFFSET              | -64 to<br>+63                           | Offset value.<br>For MODE = 0, each LSB introduces an offset of 4.34 ppm. For MODE<br>each LSB introduces an offset of 4.069 ppm. The values of 4.34 ppm<br>4.069 ppm are based on a nominal 32.768 kHz clock. The offset valu<br>coded in two's complement giving a range of +63 LSB to -64 LSB (se<br>FREQUENCY OFFSET COMPENSATION). |             |             |              |                                                  |       |                  |  |

| OFESET  | OFFSET compensation | OFFSET compensation value<br>in decimal |                                                                                                                                                                                                                                                                                                                                         | pensation   | pulses      |              | CLKOUT frequency<br>offset in ppm <sup>(1)</sup> |       |                  |  |

| OFFSET  | in decimal          |                                         |                                                                                                                                                                                                                                                                                                                                         | in steps    |             |              | mal Mode<br>ODE = 0                              | Fas   | t Mode<br>DE = 1 |  |

| 0111111 | 63                  |                                         | +63                                                                                                                                                                                                                                                                                                                                     |             |             | +            | 273.420                                          | +2    | 56.347           |  |

| 0111110 | 62                  |                                         |                                                                                                                                                                                                                                                                                                                                         | +62         |             | +            | 269.080                                          | +2    | 52.278           |  |

| :       | :                   |                                         |                                                                                                                                                                                                                                                                                                                                         | :           |             |              | :                                                |       | •                |  |

| 0000001 | 1                   |                                         |                                                                                                                                                                                                                                                                                                                                         | +1          |             |              | +4.340                                           | +     | 4.069            |  |

| 0000000 | 0                   |                                         |                                                                                                                                                                                                                                                                                                                                         | 0           |             |              | 0                                                |       | 0                |  |

| 1111111 | 127                 |                                         |                                                                                                                                                                                                                                                                                                                                         | -1          |             |              | -4.340                                           | -4    | 4.069            |  |

| 1111110 | 126                 |                                         |                                                                                                                                                                                                                                                                                                                                         | -2          |             |              | -8.680                                           | -8    | 3.138            |  |

|         | :                   |                                         |                                                                                                                                                                                                                                                                                                                                         | :           |             |              | :                                                |       |                  |  |

| 100001  | 65                  |                                         |                                                                                                                                                                                                                                                                                                                                         | -63         |             | -            | 273.420                                          | -25   | 56.347           |  |

| 1000001 |                     |                                         |                                                                                                                                                                                                                                                                                                                                         | -64         |             |              | 277.760                                          |       | 50.416           |  |

### 03h - RAM

Free RAM byte, which can be used for any purpose, for example, status byte of the system.

| Address | Function | Bit 7         | Bit 6            | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |

|---------|----------|---------------|------------------|-------|-------|-------|-------|-------|-------|--|--|

| 03h     | RAM      | RAM data      |                  |       |       |       |       |       |       |  |  |

| 030     | Reset    | 0             | 0                | 0     | 0     | 0     | 0     | 0     | 0     |  |  |

| Bit     | Symbol   | Value         | alue Description |       |       |       |       |       |       |  |  |

| 7:0     | RAM      | 00h to<br>FFh | User RAM         | I     |       |       |       |       |       |  |  |

#### **3.3. TIME AND DATE REGISTERS**

#### 04h - Seconds

This register holds the count of seconds, in two binary coded decimal (BCD) digits. Values will be from 00 to 59.

| Address | Function | Bit 7    | Bit 6                                                                                                 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |

|---------|----------|----------|-------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|--|--|

| 04h     | Seconds  | OS       | 40                                                                                                    | 20    | 10    | 8     | 4     | 2     | 1     |  |  |

| 0411    | Reset    | 1        | 0                                                                                                     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |

| Bit     | Symbol   | Value    | ue Description                                                                                        |       |       |       |       |       |       |  |  |

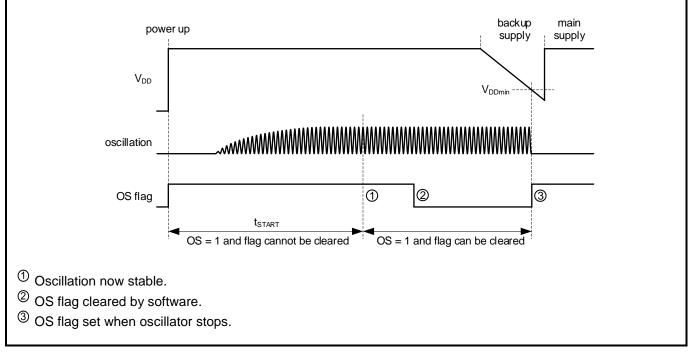

|         |          |          | Oscillator Stop (see OSCILLATOR STOP FLAG)                                                            |       |       |       |       |       |       |  |  |

| 7       | OS       | 0        | Clock integrity is guaranteed.                                                                        |       |       |       |       |       |       |  |  |

| ·       |          | 1        | Clock integrity is not guaranteed; oscillator has stopped or has been<br>interrupted. – Default value |       |       |       |       |       |       |  |  |

| 6:0     | Seconds  | 00 to 59 | Holds the count of seconds, coded in BCD format.                                                      |       |       |       |       |       |       |  |  |

#### 05h - Minutes

This register holds the count of minutes, in two binary coded decimal (BCD) digits. Values will be from 00 to 59.

| Address | Function | Bit 7    | Bit 6       | Bit 5 | Bit 4 | Bit 3       | Bit 2 | Bit 1 | Bit 0 |  |

|---------|----------|----------|-------------|-------|-------|-------------|-------|-------|-------|--|

| 05h     | Minutes  | Х        | 40          | 20    | 10    | 8           | 4     | 2     | 1     |  |

| 050     | Reset    | 0        | 0           | 0     | 0     | 0           | 0     | 0     | 0     |  |

| Bit     | Symbol   | Value    | Description |       |       |             |       |       |       |  |

| 7       | X        | 0        | Unused      |       | _     | 500011ptiol |       |       |       |  |

| 6:0     | Minutes  | 00 to 59 |             |       |       |             |       |       |       |  |

#### 06h – Hours

This register holds the count of hours, in two binary coded decimal (BCD) digits. If the 12\_24 bit is cleared (default) (see CONTROL REGISTERS, 00h - Control1) the values will be from 0 to 23. If the 12\_24 bit is set, the hour values will range from 1 to 12 and the AMPM bit will be 0 for AM hours and 1 for PM hours.

| Address         | Function                                | Bit 7   | Bit 6                                             | Bit 5         | Bit 4       | Bit 3        | Bit 2 | Bit 1 | Bit 0 |

|-----------------|-----------------------------------------|---------|---------------------------------------------------|---------------|-------------|--------------|-------|-------|-------|

|                 | Hours (24 hour mode)<br>– default value | x       | x                                                 | 20            | 10          | 8            | 4     | 2     | 1     |

| 06h             | Hours (12 hour mode)                    |         |                                                   | AMPM          | 10          | 8            | 4     | 2     | 1     |

|                 | Reset                                   | 0       | 0                                                 | 0             | 0           | 0            | 0     | 0     | 0     |

| ,               | ode), 12_24 = 0 – default value         |         |                                                   |               |             |              |       |       |       |

| Bit             | Symbol                                  | Value   |                                                   |               |             | Descriptio   | n     |       |       |

| 7:6             | X                                       | 0       | Unused                                            |               |             |              |       |       |       |

| 5:0             | Hours (24 hour mode)<br>– default value | 0 to 23 | Holds the                                         | e count of ho | ours, codec | I in BCD for | rmat. |       |       |

| ours (12 hour m | ode), 12_24 = 1                         |         |                                                   |               |             |              |       |       |       |

| Bit             | Symbol                                  | Value   |                                                   |               |             | Descriptio   | n     |       |       |

| 7:6             | Х                                       | 0       | Unused                                            |               |             |              |       |       |       |

| F               |                                         | 0       | AM hours.                                         |               |             |              |       |       |       |

| 5               | AMPM                                    | 1       | PM hours.                                         |               |             |              |       |       |       |

| 4:0             | Hours (12 hour mode)                    | 1 to 12 | 12 Holds the count of hours, coded in BCD format. |               |             |              |       |       |       |

#### 07h – Date

This register holds the current date of the month, in two binary coded decimal (BCD) digits. Values will range from 01 to 31. Leap years are correctly handled from 2000 to 2099.

| Address | Function | Bit 7    | Bit 6             | Bit 5      | Bit 4        | Bit 3       | Bit 2      | Bit 1       | Bit 0     |

|---------|----------|----------|-------------------|------------|--------------|-------------|------------|-------------|-----------|

| 07h     | Date     | Х        | Х                 | 20         | 10           | 8           | 4          | 2           | 1         |

| 07h     | Reset    | 0        | 0                 | 0          | 0            | 0           | 0          | 0           | 1         |

| Bit     | Symbol   | Value    |                   |            |              | Description | า          |             |           |

| 7:6     | Х        | 0        | Unused            |            |              |             |            |             |           |

| 5:0     | Date     | 01 to 31 | Holds the<br>= 01 | current da | te of the mo | onth, coded | in BCD for | mat. – Defa | ult value |

#### 08h - Weekday

This register holds the current day of the week. Each value represents one weekday that is assigned by the user. Values will range from 0 to 6.

| Address          | Function  | Bit 7  | Bit 6     | Bit 5     | Bit 4       | Bit 3       | Bit 2 | Bit 1 | Bit 0 |

|------------------|-----------|--------|-----------|-----------|-------------|-------------|-------|-------|-------|

| 08h              | Weekday   | Х      | Х         | Х         | Х           | Х           | 4     | 2     | 1     |

| 0011             | Reset     | 0      | 0         | 0         | 0           | 0           | 1     | 1     | 0     |

| Bit              | Symbol    | Value  |           |           |             | Description | า     |       |       |

| 7:3              | Х         | 0      | Unused    |           |             |             |       |       |       |

| 2:0              | Weekday   | 0 to 6 | Holds the | weekday o | ounter valu | e.          |       |       |       |

| Weekday          |           | Bit 7  | Bit 6     | Bit 5     | Bit 4       | Bit 3       | Bit 2 | Bit 1 | Bit 0 |

| Weekday 1        |           |        |           |           |             |             | 0     | 0     | 0     |

| Weekday 2        |           |        |           |           |             |             | 0     | 0     | 1     |

| Weekday 3        |           |        |           |           |             |             | 0     | 1     | 0     |

| Weekday 4        |           | 0      | 0         | 0         | 0           | 0           | 0     | 1     | 1     |

| Weekday 5        |           |        |           |           |             |             | 1     | 0     | 0     |

| Weekday 6        |           |        |           |           |             |             | 1     | 0     | 1     |

| Weekday 7 - Defa | ult value |        |           |           |             |             | 1     | 1     | 0     |

#### 09h - Month

This register holds the current month, in two binary coded decimal (BCD) digits. Values will range from 01 to 12.

| Address           | Function | Bit 7    | Bit 6     | Bit 5      | Bit 4       | Bit 3      | Bit 2 | Bit 1 | Bit 0 |

|-------------------|----------|----------|-----------|------------|-------------|------------|-------|-------|-------|

| 0.01-             | Month    | Х        | Х         | Х          | 10          | 8          | 4     | 2     | 1     |

| 09h               | Reset    | 0        | 0         | 0          | 0           | 0          | 0     | 0     | 1     |

| Bit               | Symbol   | Value    |           |            |             | Descriptio | n     |       |       |

| 7:5               | Х        | 0        | Unused    |            |             |            |       |       |       |

| 4:0               | Month    | 01 to 12 | Holds the | current mo | onth, coded | in BCD for | mat.  |       |       |

| Month             |          | Bit 7    | Bit 6     | Bit 5      | Bit 4       | Bit 3      | Bit 2 | Bit 1 | Bit 0 |

| January – Default | value    |          |           |            | 0           | 0          | 0     | 0     | 1     |

| February          |          |          |           |            | 0           | 0          | 0     | 1     | 0     |

| March             |          |          |           |            | 0           | 0          | 0     | 1     | 1     |

| April             |          |          |           |            | 0           | 0          | 1     | 0     | 0     |

| May               |          |          |           |            | 0           | 0          | 1     | 0     | 1     |

| June              |          | 0        | 0         | 0          | 0           | 0          | 1     | 1     | 0     |

| July              |          | 0        | 0         | 0          | 0           | 0          | 1     | 1     | 1     |

| August            |          |          |           |            | 0           | 1          | 0     | 0     | 0     |

| September         |          |          |           |            | 0           | 1          | 0     | 0     | 1     |

| October           |          |          |           |            | 1           | 0          | 0     | 0     | 0     |

| November          |          |          |           |            | 1           | 0          | 0     | 0     | 1     |

| December          |          |          |           |            | 1           | 0          | 0     | 1     | 0     |

#### 0Ah - Year

This register holds the current year, in two binary coded decimal (BCD) digits. Values will range from 00 to 99. Leap years are correctly handled from 2000 to 2099.

| Address | Function | Bit 7    | Bit 6     | Bit 5       | Bit 4        | Bit 3       | Bit 2 | Bit 1 | Bit 0 |

|---------|----------|----------|-----------|-------------|--------------|-------------|-------|-------|-------|

| 046     | Year     | 80       | 40        | 20          | 10           | 8           | 4     | 2     | 1     |

| 0Ah     | Reset    | 0        | 0         | 0           | 0            | 0           | 0     | 0     | 0     |

| Bit     | Symbol   | Value    |           |             | [            | Descriptior | ı     |       |       |

| 7:0     | Year     | 00 to 99 | Holds the | current yea | ar, coded in | BCD forma   | at.   |       |       |

#### **3.4. ALARM REGISTERS**

#### 0Bh – Seconds Alarm

This register holds the Seconds Alarm Enable bit AE\_S and the alarm value for seconds, in two binary coded decimal (BCD) digits. Values will range from 00 to 59.

| Address | Function      | Bit 7                                                            | Bit 6   | Bit 5      | Bit 4      | Bit 3       | Bit 2    | Bit 1 | Bit 0 |

|---------|---------------|------------------------------------------------------------------|---------|------------|------------|-------------|----------|-------|-------|

| 0Bh     | Seconds Alarm | AE_S                                                             | 40      | 20         | 10         | 8           | 4        | 2     | 1     |

| UDII    | Reset         | 1                                                                | 0       | 0          | 0          | 0           | 0        | 0     | 0     |

| Bit     | Symbol        | Value                                                            |         |            | I          | Description | ı        |       |       |

|         |               |                                                                  | Sec     | onds Alarm | Enable bit | (see ALAR   | M FUNCTI | ON)   |       |

| 7       | AE_S          | 0                                                                | Enabled |            |            |             |          |       |       |

|         |               | 1 Disabled – Default value                                       |         |            |            |             |          |       |       |

| 6:0     | Seconds Alarm | 00 to 59 Holds the alarm value for seconds, coded in BCD format. |         |            |            |             |          |       |       |

#### 0Ch – Minutes Alarm

This register holds the Minutes Alarm Enable bit AE\_M and the alarm value for minutes, in two binary coded decimal (BCD) digits. Values will range from 00 to 59.

| Address | Function      | Bit 7                      | Bit 6     | Bit 5      | Bit 4        | Bit 3        | Bit 2    | Bit 1 | Bit 0 |

|---------|---------------|----------------------------|-----------|------------|--------------|--------------|----------|-------|-------|

| 0Ch     | Minutes Alarm | AE_M                       | 40        | 20         | 10           | 8            | 4        | 2     | 1     |

| UCH     | Reset         | 1                          | 0         | 0          | 0            | 0            | 0        | 0     | 0     |

| Bit     | Symbol        | Value Description          |           |            |              |              |          |       |       |

|         |               |                            | Min       | utes Alarm | Enable bit   | (see ALARI   | M FUNCTI | ON)   |       |

| 7       | AE_M          | 0                          | Enabled   |            |              |              |          |       |       |

|         |               | 1 Disabled – Default value |           |            |              |              |          |       |       |

| 6:0     | Minutes Alarm | 00 to 59                   | Holds the | alarm valu | e for minute | es, coded ir | BCD form | at.   |       |

#### 0Dh – Hours Alarm

This register holds the Hours Alarm Enable bit AE\_H and the alarm value for hours, in two binary coded decimal (BCD) digits. If the 12\_24 bit is cleared (default value) (see CONTROL REGISTERS, 00h - Control1) the values will range from 00 to 23. If the 12\_24 bit is set, the hour values will be from 01 to 12 and the AMPM bit will be 0 for AM hours and 1 for PM hours.

| Address            | Function                                      | Bit 7    | Bit 6                    | Bit 5                          | Bit 4        | Bit 3        | Bit 2      | Bit 1 | Bit 0 |  |

|--------------------|-----------------------------------------------|----------|--------------------------|--------------------------------|--------------|--------------|------------|-------|-------|--|

|                    | Hours Alarm (24 hour<br>mode) – default value | AE H     | х                        | 20                             | 10           | 8            | 4          | 2     | 1     |  |

| 0Dh                | Hours Alarm (12 hour mode)                    |          | ^                        | AMPM                           | 10           | 8            | 4          | 2     | 1     |  |

|                    | Reset                                         | 1        | 0                        | 0                              | 0            | 0            | 0          | 0     | 0     |  |

| Hours Alarm (24 ho | our mode), 12_24 = 0 – default                | value    |                          |                                |              |              |            |       |       |  |

| Bit                | Symbol                                        | Value    |                          |                                |              | Descriptio   | n          |       |       |  |

|                    |                                               |          | Ho                       | ours Alarm I                   | Enable bit ( | see ALARN    | I FUNCTIC  | N)    |       |  |

| 7                  | AE_H                                          | 0        | Enabled                  |                                |              |              |            |       |       |  |

|                    |                                               | 1        | Disabled – Default value |                                |              |              |            |       |       |  |

| 6                  | X                                             | 0        | Unused                   |                                |              |              |            |       |       |  |

| 5:0                | Hours Alarm (24 hour<br>mode) – default value | 00 to 23 |                          |                                |              |              |            |       |       |  |

| Hours Alarm (12 ho | our mode), 12_24 = 1                          |          |                          |                                |              |              |            |       |       |  |

| Bit                | Symbol                                        | Value    |                          |                                |              | Descriptio   | n          |       |       |  |

|                    |                                               |          | Ho                       | ours Alarm I                   | Enable bit ( | see ALARN    | I FUNCTIC  | N)    |       |  |

| 7                  | AE_H                                          | 0        | Enabled                  |                                |              |              |            |       |       |  |

|                    |                                               | 1        | Disabled                 | <ul> <li>Default va</li> </ul> | alue         |              |            |       |       |  |

| 6                  | X                                             | 0        | Unused                   |                                |              |              |            |       |       |  |

| F                  |                                               | 0        | AM hours                 | 3.                             |              |              |            |       |       |  |

| 5                  | AMPM                                          | 1        | 1 PM hours.              |                                |              |              |            |       |       |  |

| 4:0                | Hours Alarm (12 hour mode)                    | 01 to 12 | Holds the                | e alarm valu                   | e for hours  | , coded in E | SCD format |       |       |  |

#### 0Eh - Date Alarm

This register holds the Date Alarm Enable bit AE\_D and the alarm value for the date, in two binary coded decimal (BCD) digits. Values will range from 01 to 31.

| Address | Function   | Bit 7    | Bit 6                                      | Bit 5                          | Bit 4        | Bit 3         | Bit 2      | Bit 1 | Bit 0 |

|---------|------------|----------|--------------------------------------------|--------------------------------|--------------|---------------|------------|-------|-------|

| 0Eh     | Date Alarm | AE_D     | Х                                          | 20                             | 10           | 8             | 4          | 2     | 1     |

| UEII    | Reset      | 1        | 0                                          | 0                              | 0            | 0             | 0          | 0     | 0     |

| Bit     | Symbol     | Value    |                                            |                                |              | Description   | า          |       |       |

|         |            |          | Date Alarm Enable bit (see ALARM FUNCTION) |                                |              |               |            |       |       |

| 7       | AE_D       | 0        | Enabled                                    |                                |              |               |            |       |       |

|         |            | 1        | Disabled -                                 | <ul> <li>Default va</li> </ul> | alue         |               |            |       |       |

| 6       | Х          | 0        | 0 Unused                                   |                                |              |               |            |       |       |

| 5:0     | Date Alarm | 01 to 31 | Holds the                                  | alarm valu                     | e for the da | ite, coded ir | n BCD form | at.   |       |

#### 0Fh – Weekday Alarm

This register holds the Weekday Alarm Enable bit AE\_W and the alarm value for the weekday, in two binary coded decimal (BCD) digits. Values will range from 0 to 6.

| Address | Function      | Bit 7                                         | Bit 6      | Bit 5                          | Bit 4       | Bit 3      | Bit 2      | Bit 1 | Bit 0 |

|---------|---------------|-----------------------------------------------|------------|--------------------------------|-------------|------------|------------|-------|-------|

| 0Fh     | Weekday Alarm | AE_W                                          | Х          | Х                              | Х           | Х          | 4          | 2     | 1     |

| UFN     | Reset         | 1                                             | 0          | 0                              | 0           | 0          | 0          | 0     | 0     |

| Bit     | Symbol        | Value                                         |            |                                |             | Descriptio | า          |       |       |

|         |               | Weekday Alarm Enable bit (see ALARM FUNCTION) |            |                                |             |            |            |       |       |

| 7       | AE_W          | 0                                             | Enabled    |                                |             |            |            |       |       |

|         |               | 1                                             | Disabled - | <ul> <li>Default va</li> </ul> | alue        |            |            |       |       |

| 6:3     | Х             | 0 Unused                                      |            |                                |             |            |            |       |       |

| 2:0     | Weekday Alarm | 0 to 6                                        | Holds the  | weekday a                      | larm value, | coded in B | CD format. |       |       |

#### RV-8063-C8

#### **3.5. TIMER REGISTERS**

#### 10h – Timer Value

This register holds the current value of the Countdown Timer. It may be loaded with the desired starting value when the Countdown Timer is stopped.

| Address | Function    | Bit 7         | Bit 6    | Bit 5       | Bit 4       | Bit 3       | Bit 2      | Bit 1 | Bit 0 |

|---------|-------------|---------------|----------|-------------|-------------|-------------|------------|-------|-------|

| 10h     | Timer Value | 128           | 64       | 32          | 16          | 8           | 4          | 2     | 1     |

| TON     | Reset       | 0             | 0        | 0           | 0           | 0           | 0          | 0     | 0     |

| Bit     | Symbol      | Value         |          |             | I           | Description | า          |       |       |

| 7:0     | Timer Value | 00h to<br>FFh | Countdow | vn Timer Va | alue (see C | OUNTDOW     | 'N TIMER F |       | )     |

Countdown Period in seconds:

#### 11h – Timer Mode

This register controls the Countdown Timer function.

| Address | Function   | Bit 7                                                                                                                                      | Bit 6                          | Bit 5                         | Bit 4       | Bit 3       | Bit 2      | Bit 1                 | Bit 0 |

|---------|------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------------------------|-------------|-------------|------------|-----------------------|-------|

| 4.41    | Timer Mode | Х                                                                                                                                          | Х                              | Х                             | T           | D           | TE         | TIE                   | TI_TF |

| 11h     | Reset      | 0                                                                                                                                          | 0                              | 0                             | 1           | 1           | 0          | 0                     | 0     |

| Bit     | Symbol     | Value                                                                                                                                      |                                |                               |             | Descriptio  | n          |                       |       |

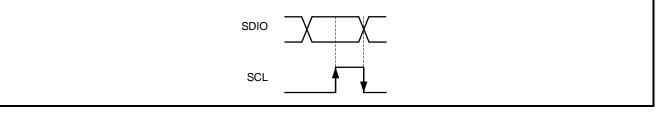

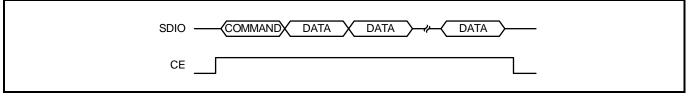

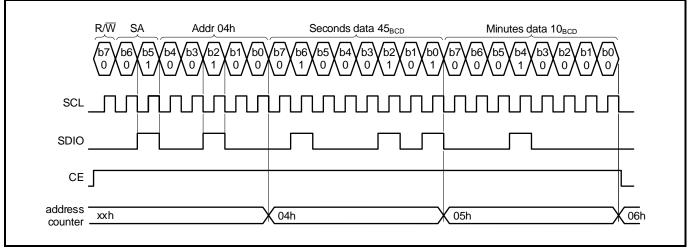

| 7:5     | Х          | 0                                                                                                                                          | Unused                         |                               |             |             |            |                       |       |